背景

RISC-V是一种开放式指令集架构,其设计目标是简洁、模块化和可扩展性,以适应广泛的计算需求。浮点运算在现代计算中扮演着关键角色,尤其是在科学计算、工程模拟和图形处理等领域。为了有效地管理浮点运算中的各种操作模式和异常,RISC-V引入了浮点控制状态寄存器(fcsr)。fcsr不仅负责处理舍入模式,还记录浮点运算过程中可能发生的异常。

介绍

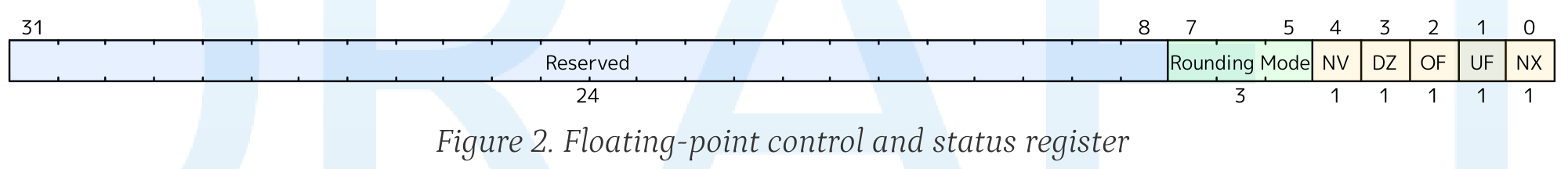

浮点控制状态寄存器(fcsr)是RISC-V中一个32位的控制和状态寄存器,专门用于管理浮点运算的舍入模式和异常标志。fcsr由两个主要部分组成:

舍入模式(frm):

舍入模式决定了浮点运算结果如何被舍入。RISC-V支持多种舍入模式,包括:

| 舍入模式名称 | 缩写 | 编码 |

|---|---|---|

| 向最近偶数舍入 | RNE | 000 |

| 向零舍入 | RTZ | 001 |

| 向负无穷舍入 | RDN | 010 |

| 向正无穷舍入 | RUP | 011 |

| 向最大尾数舍入 | RMM | 100 |

舍入模式可以是静态的,即在指令中直接指定,也可以是动态的,通过frm字段进行选择。

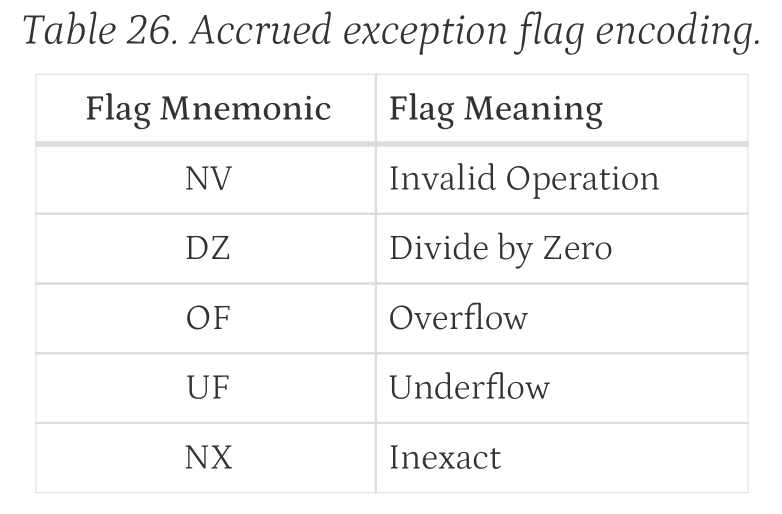

异常标志(fflags):

fflags记录了浮点运算中可能发生的异常,自上次软件重置以来的任何浮点算术指令都可能触发这些标志:

| 异常标志名称 | 缩写 | 含义 |

|---|---|---|

| 非法操作 | NV | Invalid Operation |

| 除以零 | DZ | Divide by Zero |

| 上溢 | OF | Overflow |

| 下溢 | UF | Underflow |

| 结果不精确 | NX | Inexact |

这些标志帮助程序员识别和处理浮点运算中的异常情况,提高程序的健壮性和可靠性。

fcsr寄存器可以通过特定的伪指令(如FRCSR和FSCSR)进行读写,便于程序灵活地调整舍入模式和监控异常状态。此外,寄存器的不同字段可以通过单独的CSR地址访问,以实现更精细的控制。

设计选择与实现

RISC-V基础指令集架构(ISA)及其浮点扩展(F扩展)选择不支持在浮点异常标志被设置时生成陷阱(trap)。这意味着,当发生浮点异常时,系统不会自动中断程序的执行,而是需要软件显式检查这些标志,以便决定接下来的处理步骤。这种设计选择有以下几个考虑:

- 保持ISA的简洁性:通过避免在异常情况下自动生成陷阱,RISC-V能够保持指令集的简单性和一致性,减少对硬件实现的复杂性要求。

- 灵活的异常处理:程序员可以根据具体应用的需求,通过软件检查异常标志来实现自定义的异常处理逻辑。这种灵活性允许在不同的上下文中采取不同的措施,而不是依赖于硬件的固定行为。

简化控制流:虽然曾考虑在指令集中增加由浮点异常标志直接控制的分支指令,但最终决定不支持这些特性,以避免增加额外的复杂性。

本文由 BWonder 创作,采用 知识共享署名4.0 国际许可协议进行许可。

本站文章除注明转载/出处外,均为本站原创或翻译,转载前请务必署名。